# **Surface Mount PIN Diodes**

## Technical Data

### HSMP-386x Series

### Features

- Unique Configurations in Surface Mount Packages

- Add Flexibility

- Save Board Space

- Reduce Cost

- Switching

- Low Distortion Switching

- Low Capacitance

- Attenuating

- Low Current Attenuating for Less Power Consumption

- Matched Diodes for Consistent Performance

- Better Thermal Conductivity for Higher Power Dissipation

- Low Failure in Time (FIT) Rate<sup>[1]</sup>

- Lead-free Option Available

#### Note:

1. For more information see the Surface Mount PIN Reliability Data Sheet.

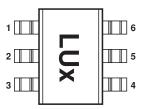

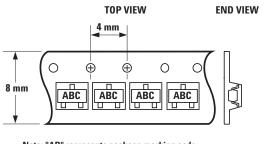

### Pin Connections and Package Marking, SOT-363

#### Notes:

- 1. Package marking provides orientation, identification, and date code.

- 2. See "Electrical Specifications" for appropriate package marking.

### **Description/Applications**

The HSMP-386x series of general purpose PIN diodes are designed for two classes of applications. The first is attenuators where current consumption is the most important design consideration. The second application for this series of diodes is in switches where low capacitance is the driving issue for the designer.

The HSMP-386x series Total Capacitance ( $C_T$ ) and Total Resistance ( $R_T$ ) are typical specifications. For applications that require guaranteed performance, the general purpose HSMP-383x series is recommended.

A SPICE model is not available for PIN diodes as SPICE does not provide for a key PIN diode characteristic, carrier lifetime.

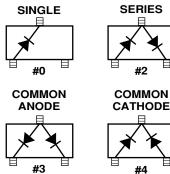

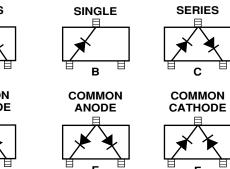

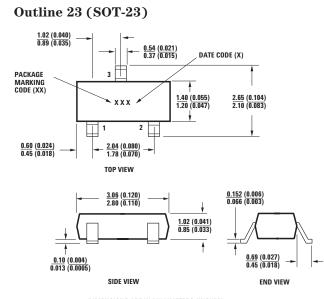

### Package Lead Code Identification, SOT-23 (Top View)

Package Lead Code Identification, SOT-323 (Top View)

Package Lead Code Identification, SOT-363 (Top View)

### Absolute Maximum Ratings<sup>[1]</sup> $T_C = +25^{\circ}C$

| Symbol           | Parameter                         | Unit | SOT-23     | SOT-323    |

|------------------|-----------------------------------|------|------------|------------|

| If               | Forward Current (1 µs Pulse)      | Amp  | 1          | 1          |

| P <sub>IV</sub>  | Peak Inverse Voltage              | V    | 50         | 50         |

| Tj               | Junction Temperature              | °C   | 150        | 150        |

| T <sub>stg</sub> | Storage Temperature               | °C   | -65 to 150 | -65 to 150 |

| $\theta_{jc}$    | Thermal Resistance <sup>[2]</sup> | °C/W | 500        | 150        |

*ESD WARNING:* Handling Precautions Should Be Taken To Avoid Static Discharge.

#### Notes:

1. Operation in excess of any one of these conditions may result in permanent damage to the device.

2.  $T_{\rm C}$  = +25°C, where  $T_{\rm C}$  is defined to be the temperature at the package pins where contact is made to the circuit board.

### Electrical Specifications $T_c = 25^{\circ}C$ , each diode

PIN General Purpose Diodes, Typical Specifications  $T_{\rm A}$  = 25°C

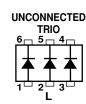

| Part Number<br>HSMP-                                                         | Package<br>Marking<br>Code                                                                                                                | Lead<br>Code                              | Configuration                                                                                                                | Minimum<br>Breakdown<br>Voltage V <sub>BR</sub> (V)                                           | Typical<br>Series Resistance<br>R <sub>S</sub> (Ω)                                                              | Typical<br>Total Capacitance<br>C <sub>T</sub> (pF) |

|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|

| 3860<br>3862<br>3863<br>3864<br>386B<br>386C<br>386E<br>386F<br>386F<br>386L | $egin{array}{c} L0^{[1]}\ L2^{[1]}\ L3^{[1]}\ L4^{[1]}\ L0^{[2]}\ L2^{[2]}\ L3^{[2]}\ L3^{[2]}\ L4^{[2]}\ L4^{[2]}\ L4^{[2]} \end{array}$ | 0<br>2<br>3<br>4<br>B<br>C<br>E<br>F<br>L | Single<br>Series<br>Common Anode<br>Common Cathode<br>Single<br>Series<br>Common Anode<br>Common Cathode<br>Unconnected Trio | 50                                                                                            | 3.0/1.5*                                                                                                        | 0.20                                                |

| Test Conditions                                                              |                                                                                                                                           |                                           |                                                                                                                              | $\begin{array}{l} V_{\rm R} = V_{\rm BR} \\ Measure \\ I_{\rm R} \leq 10 \ \mu A \end{array}$ | $\begin{split} I_{\rm F} &= 10 \text{ mA} \\ f &= 100 \text{ MHz} \\ I_{\rm F} &= 100 \text{ mA}^* \end{split}$ | $V_R = 50 V$<br>f = 1 MHz                           |

#### Notes:

1. Package marking code is laser marked.

| Part Number<br>HSMP-                                 | Total Resistance $\mathbf{R}_{\mathrm{T}}(\Omega)$ | Carrier Lifetime<br>τ (ns)                               | Reverse Recovery Time<br>T <sub>rr</sub> (ns)                                                                 | Total Capacitance<br>C <sub>T</sub> (pF)                |

|------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| 386x                                                 | 22                                                 | 500                                                      | 80                                                                                                            | 0.20                                                    |

| Test Conditions $I_F = 1 \text{ mA}$<br>f = 100  MHz |                                                    | $I_{\rm F} = 50 \text{ mA}$ $T_{\rm R} = 250 \text{ mA}$ | $\begin{array}{c} V_{\rm R} = 10 \ {\rm V} \\ I_{\rm F} = 20 \ {\rm mA} \\ 90\% \ {\rm Recovery} \end{array}$ | $\begin{array}{l} V_{R}=50 \ V\\ f=1 \ MHz \end{array}$ |

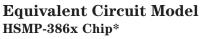

HSMP-386x Typical Parameters at  $T_C = 25^{\circ}C$

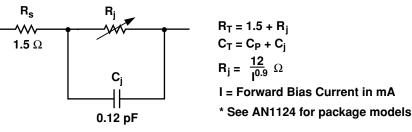

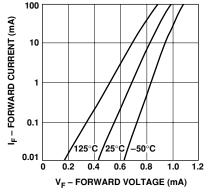

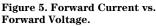

Typical Performance,  $T_C = 25^{\circ}C$ , each diode

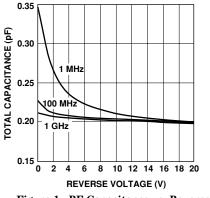

Figure 1. RF Capacitance vs. Reverse Bias.

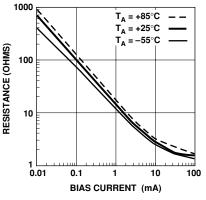

Figure 2. Typical RF Resistance vs. Forward Bias Current.

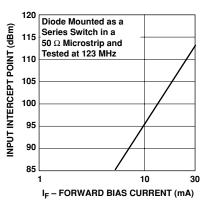

Figure 3. 2nd Harmonic Input Intercept Point vs. Forward Bias Current for Switch Diodes.

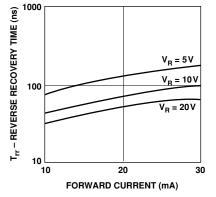

Figure 4. Reverse Recovery Time vs. Forward Current for Various Reverse Voltages.

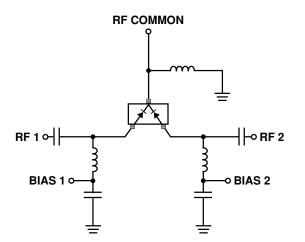

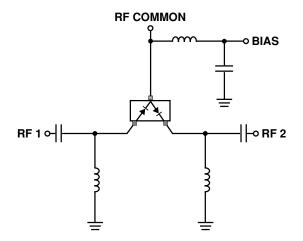

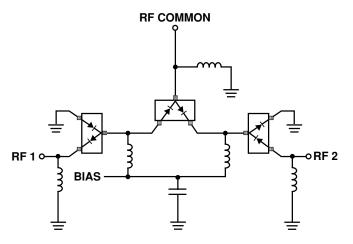

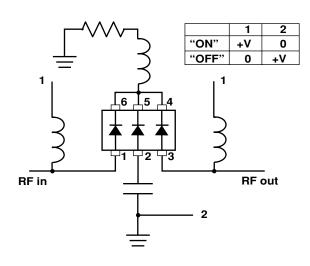

Figure 6. Simple SPDT Switch, Using Only Positive Current.

Figure 8. Switch Using Both Positive and Negative Current.

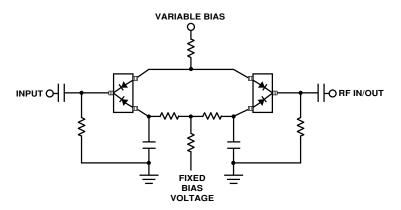

Figure 10. Four Diode  $\pi$  Attenuator. See AN1048 for details.

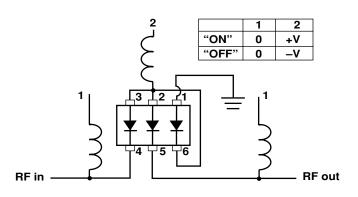

Figure 7. High Isolation SPDT Switch, Dual Bias.

Figure 9. Very High Isolation SPDT Switch, Dual Bias.

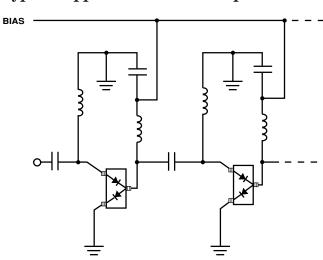

Figure 11. High Isolation SPST Switch (Repeat Cells as Required).

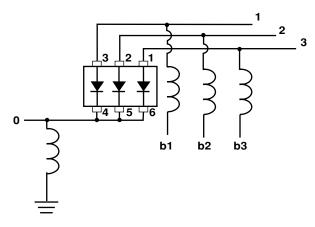

Figure 13. HSMP-386L used in a SP3T Switch.

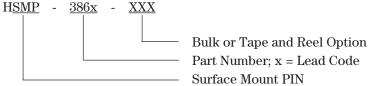

#### **Ordering Information**

Specify part number followed by option. For example:

#### **Option Descriptions**

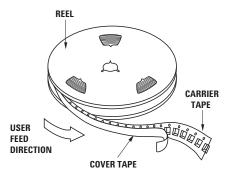

-BLK = Bulk, 100 pcs. per antistatic bag -TR1 = Tape and Reel, 3000 devices per 7" reel -TR2 = Tape and Reel, 10,000 devices per 13" reel

Tape and Reeling conforms to Electronic Industries RS-481, "Taping of Surface Mounted Components for Automated Placement."

For lead-free option, the part number will have the character "G" at the end, eg. -TR2G for a 10K pc lead-free reel.

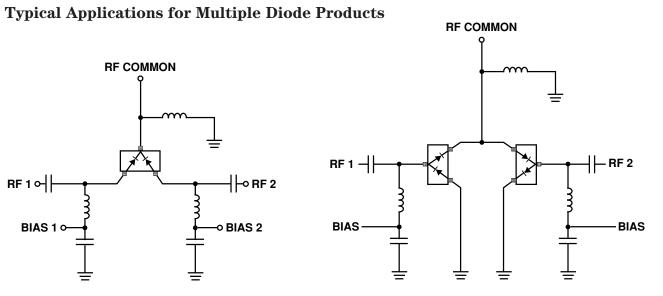

Figure 12. HSMP-386L Unconnected Trio used in a Positive Voltage, High Isolation Switch.

Figure 14. HSMP-386L Unconnected Trio used in a Dual Voltage, High Isolation Switch.

### Typical Applications for Multiple Diode Products (continued)

#### Assembly Information SOT-323 PCB Footprint

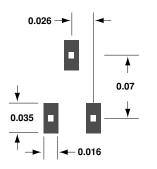

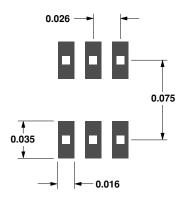

Recommended PCB pad layouts for the miniature SOT packages are shown in Figures 15, 16, 17. These layouts provide ample allowance for package placement by automated assembly equipment without adding parasitics that could impair the performance.

Figure 15. PCB Pad Layout, SOT-323. (dimensions in inches).

Figure 16. PCB Pad Layout, SOT-363. (dimensions in inches).

#### **SMT Assembly**

Reliable assembly of surface mount components is a complex process that involves many material, process, and equipment factors, including: method of heating (e.g., IR or vapor phase reflow, wave soldering, etc.) circuit board material, conductor thickness and pattern, type of solder alloy, and the thermal conductivity and thermal mass of components. Components with a low mass, such as the SOT package, will reach solder reflow temperatures faster than those with a greater mass.

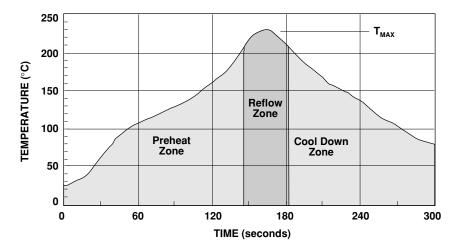

Agilent's diodes have been qualified to the time-temperature profile shown in Figure 18. This profile is representative of an IR reflow type of surface mount assembly process.

After ramping up from room temperature, the circuit board with components attached to it (held in place with solder paste) passes through one or more preheat zones. The preheat zones increase the temperature of the board and components to prevent thermal shock and begin evaporating solvents from the solder paste. The reflow zone briefly elevates the temperature sufficiently to produce a reflow of the solder.

The rates of change of temperature for the ramp-up and cooldown zones are chosen to be low enough to not cause deformation of the board or damage to components due to thermal shock. The maximum temperature in the reflow zone ( $T_{MAX}$ ) should not exceed 235°C.

These parameters are typical for a surface mount assembly process for Agilent diodes. As a general guideline, the circuit board and components should be exposed only to the minimum temperatures and times necessary to achieve a uniform reflow of solder.

Figure 18. Surface Mount Assembly Profile.

6

Figure 17. PCB Pad Layout, SOT-23.

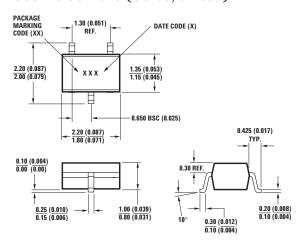

### Package Dimensions Outline SOT-323 (SC-70, 3 Lead)

DIMENSIONS ARE IN MILLIMETERS (INCHES)

DIMENSIONS ARE IN MILLIMETERS (INCHES)

#### PACKAGE MARKING CODE (XX) 1.30 (0.051) REF. DATE CODE (X) Π Ĥ 2.20 (0.087) 2.00 (0.079) 1.35 (0.053) 1.15 (0.045) ххх Ħ Å 0.650 BSC (0.025) 0.425 (0.017) TYP $\begin{array}{c} 0.10 \\ \overline{0.00} \\ \overline{0.00} \end{array}$ (0.004) 0.30 REF. f 1.00 (0.039) 0.80 (0.031) 0.20 (0.008) 0.10 (0.004) 0.25 (0.010) 0.15 (0.006) 0.30 (0.012) 0.10 (0.004) 10

#### DIMENSIONS ARE IN MILLIMETERS (INCHES)

### **Package Characteristics**

| Lead Material Co              | pper (SOT-323/363); Alloy 42 (SOT-23) |

|-------------------------------|---------------------------------------|

| Lead Finish                   | Tin-Lead 85-15%                       |

| Maximum Soldering Temperature |                                       |

| Minimum Lead Strength         |                                       |

| Typical Package Inductance    |                                       |

| Typical Package Capacitance   |                                       |

#### **Outline 363 (SC-70, 6 Lead)**

#### **Device Orientation**

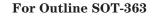

For Outlines SOT-23, -323

Note: "AB" represents package marking code. "C" represents date code.

Note: "AB" represents package marking code. "C" represents date code.

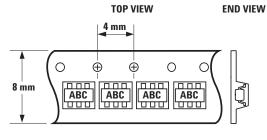

### **Tape Dimensions and Product Orientation** For Outline SOT-23

|                                   | DESCRIPTION                                 | SYMBOL         | SIZE (mm)                           | SIZE (INCHES)                       |

|-----------------------------------|---------------------------------------------|----------------|-------------------------------------|-------------------------------------|

| CAVITY                            | LENGTH                                      | A <sub>0</sub> | $\textbf{3.15} \pm \textbf{0.10}$   | $\textbf{0.124} \pm \textbf{0.004}$ |

|                                   | WIDTH                                       | B <sub>0</sub> | $\textbf{2.77} \pm \textbf{0.10}$   | $\textbf{0.109} \pm \textbf{0.004}$ |

|                                   | DEPTH                                       | KO             | $\textbf{1.22} \pm \textbf{0.10}$   | $\textbf{0.048} \pm \textbf{0.004}$ |

|                                   | PITCH                                       | Р              | $\textbf{4.00} \pm \textbf{0.10}$   | $\textbf{0.157} \pm \textbf{0.004}$ |

|                                   | BOTTOM HOLE DIAMETER                        | D <sub>1</sub> | 1.00 + 0.05                         | $\textbf{0.039} \pm \textbf{0.002}$ |

| PERFORATION                       | DIAMETER                                    | D              | 1.50 + 0.10                         | 0.059 + 0.004                       |

|                                   | PITCH                                       | Po             | $\textbf{4.00} \pm \textbf{0.10}$   | $\textbf{0.157} \pm \textbf{0.004}$ |

|                                   | POSITION                                    | E              | $\textbf{1.75} \pm \textbf{0.10}$   | $\textbf{0.069} \pm \textbf{0.004}$ |

| CARRIER TAPE                      | WIDTH                                       | w              | 8.00+0.30-0.10                      | 0.315+0.012-0.004                   |

|                                   | THICKNESS                                   | t1             | $\textbf{0.229} \pm \textbf{0.013}$ | $0.009 \pm 0.0005$                  |

| DISTANCE<br>BETWEEN<br>CENTERLINE | CAVITY TO PERFORATION<br>(WIDTH DIRECTION)  | F              | $\textbf{3.50} \pm \textbf{0.05}$   | $\textbf{0.138} \pm \textbf{0.002}$ |

|                                   | CAVITY TO PERFORATION<br>(LENGTH DIRECTION) | P <sub>2</sub> | $\textbf{2.00} \pm \textbf{0.05}$   | $\textbf{0.079} \pm \textbf{0.002}$ |

8

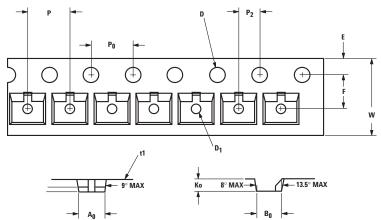

#### For Outlines SOT-323, -363 D P<sub>2</sub> Po + ÷ ÷ + (Ŧ Dı t1 (CARRIER TAPE THICKNESS) T<sub>t</sub> (COVER TAPE THICKNESS) KO An Δn 1 - A<sub>0</sub> DESCRIPTION SYMBOL SIZE (mm) SIZE (INCHES) CAVITY LENGTH 2.40 ± 0.10 0.094 ± 0.004 A WIDTH $\textbf{2.40} \pm \textbf{0.10}$ $\textbf{0.094} \pm \textbf{0.004}$ B<sub>0</sub> K<sub>0</sub> DEPTH $\textbf{1.20} \pm \textbf{0.10}$ $\textbf{0.047} \pm \textbf{0.004}$ PITCH Р $\textbf{4.00} \pm \textbf{0.10}$ $\textbf{0.157} \pm \textbf{0.004}$ BOTTOM HOLE DIAMETER D<sub>1</sub> 1.00 + 0.25 0.039 + 0.010 PERFORATION DIAMETER $1.55 \pm 0.05$ $\textbf{0.061} \pm \textbf{0.002}$ D PITCH $\textbf{0.157} \pm \textbf{0.004}$ $\textbf{4.00} \pm \textbf{0.10}$ Po POSITION $\textbf{1.75} \pm \textbf{0.10}$ $\textbf{0.069} \pm \textbf{0.004}$

## Tape Dimensions and Product Orientation

w

t<sub>1</sub>

C

Τt

F

P<sub>2</sub>

An

$\textbf{8.00} \pm \textbf{0.30}$

$\textbf{0.254} \pm \textbf{0.02}$

$\textbf{5.4} \pm \textbf{0.10}$

$\textbf{3.50} \pm \textbf{0.05}$

$\textbf{2.00} \pm \textbf{0.05}$

8°C MAX

10°C MAX

$\textbf{0.062} \pm \textbf{0.001}$

$\textbf{0.315} \pm \textbf{0.012}$

$0.205 \pm 0.004$

$\textbf{0.138} \pm \textbf{0.002}$

$\textbf{0.079} \pm \textbf{0.002}$

$\textbf{0.0100} \pm \textbf{0.0008}$

$\textbf{0.0025} \pm \textbf{0.00004}$

CARRIER TAPE

COVER TAPE

DISTANCE

ANGLE

WIDTH

THICKNESS

WIDTH TAPE THICKNESS

CAVITY TO PERFORATION

FOR SOT-323 (SC70-3 LEAD)

FOR SOT-363 (SC70-6 LEAD)

(WIDTH DIRECTION) CAVITY TO PERFORATION (LENGTH DIRECTION)

#### www.agilent.com/semiconductors

For product information and a complete list of distributors, please go to our web site.

For technical assistance call:

Americas/Canada: +1 (800) 235-0312 or (916) 788-6763

Europe: +49 (0) 6441 92460

China: 10800 650 0017 Hong Kong: (65) 6756 2394

India, Australia, New Zealand: (65) 6755 1939

Japan: (+81 3) 3335-8152(Domestic/International), or 0120-61-1280(Domestic Only)

Korea: (65) 6755 1989

Singapore, Malaysia, Vietnam, Thailand, Philippines, Indonesia: (65) 6755 2044

Taiwan: (65) 6755 1843

Data subject to change. Copyright © 2004 Agilent Technologies, Inc. Obsoletes 5988-7917EN March 24, 2004 5989-0485EN